# Digital Logic

# **Published By:**

# Physics Wallah

**ISBN:** 978-93-94342-39-2

Mobile App:Physics Wallah (Available on Play Store)

Website:

**Email:**

support@pw.live

# **Rights**

All rights will be reserved by Publisher. No part of this book may be used or reproduced in any manner whatsoever without the written permission from author or publisher.

In the interest of student's community:

Circulation of soft copy of Book(s) in PDF or other equivalent format(s) through any social media channels, emails, etc. or any other channels through mobiles, laptops or desktop is a criminal offence. Anybody circulating, downloading, storing, soft copy of the book on his device(s) is in breach of Copyright Act. Further Photocopying of this book or any of its material is also illegal. Do not download or forward in case you come across any such soft copy material.

# Disclaimer

A team of PW experts and faculties with an understanding of the subject has worked hard for the books.

While the author and publisher have used their best efforts in preparing these books. The content has been checked for accuracy. As the book is intended for educational purposes, the author shall not be responsible for any errors contained in the book.

The publication is designed to provide accurate and authoritative information with regard to the subject matter covered.

This book and the individual contribution contained in it are protected under copyright by the publisher.

(This Module shall only be Used for Educational Purpose.)

# **Digital Logic**

| 1. | Logic Gate                       | 3.1 - 3.12  |

|----|----------------------------------|-------------|

| 2. | Minimization of Boolean Function | 3.13 - 3.22 |

| 3. | Combinational Circuits           | 3.23 - 3.42 |

| 4. | Sequential Logic Circuits        | 3.43 - 3.67 |

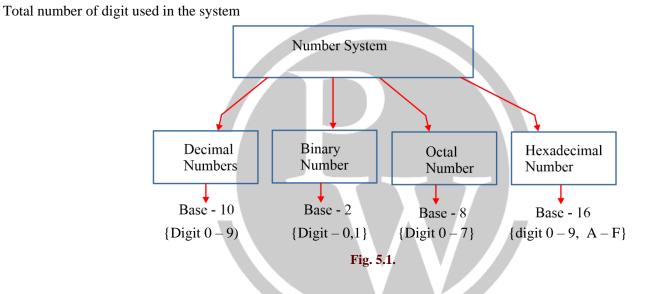

| 5. | Number System                    | 3.68 – 3.75 |

# LOGIC GATE

# **1.1. Logic Operations**

In Boolean algebra, all the algebraic functions performed is logical. The AND, OR and NOT are the basic operations that are performed in Boolean algebra. There are some derived operations such as NAND, NOR, EX-OR, EX-NOR that are also performed in Boolean algebra.

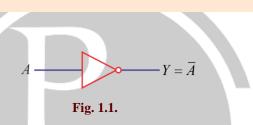

#### 1.1. NOT Operation

Symbol:

$$A \xrightarrow{\text{NOT}} \overline{A}$$

or  $A'$  (Complementation law)

and  $\overline{A} = A \Rightarrow$  Double complementation law

#### Truth table for NOT operation

| Input | Output             |  |

|-------|--------------------|--|

| A     | $Y = \overline{A}$ |  |

| 0     | 1                  |  |

| 1     | 0                  |  |

A NOT gate can be represented using switch whose circuit representation is shown in figure below.

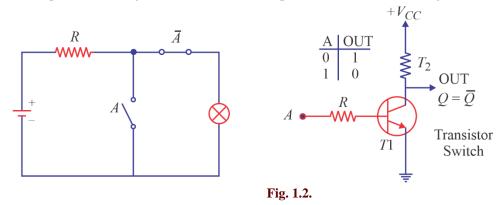

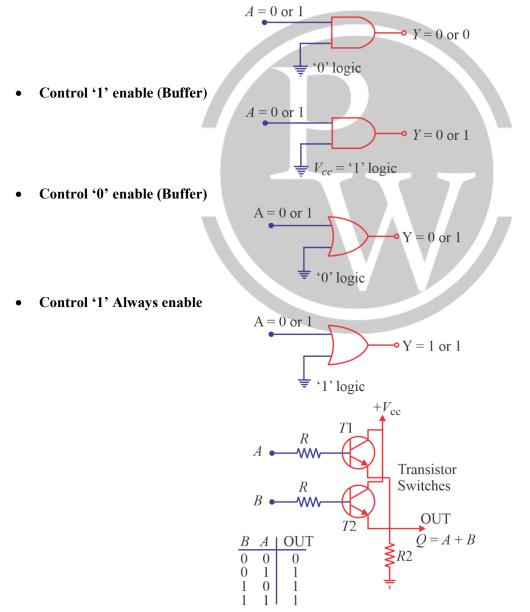

A buffer is a basic logic gate that passes its input, unchanged, to its output. Its behaviour is the opposite of a NOT gate.

The main purpose of a buffer is to regenerate the input, usually using a strong high and a strong low. Buffers are also used to increase the propagation delay of circuits by driving the large capacitive loads.

#### 1.1.2. AND Operation

Symbol:

$$A.A = A, A.0 = 0, A.1 = A, A\overline{A} = 0$$

$$A = A, A.0 = 0, A.1 = A, A\overline{A} = 0$$

$$A = A, A.0 = 0, A.1 = A, A\overline{A} = 0$$

$$A = A, A.0 = 0, A.1 = A, A\overline{A} = 0$$

$$A = A, B = A, A\overline{A} = 0$$

$$A = B = A, B$$

$$A = A, A.0 = 0, A.1 = A, A\overline{A} = 0$$

$$A = B = A, B$$

$$A = A$$

#### 1.1.3. OR Operation

Symbol:

$$A \longrightarrow A + B$$

$$A + A = A, A + 0 = A, A + 1 = 1, A + \overline{A} = 1$$

#### **Truth table for OR operation:**

|   | Input | Output                                 |  |

|---|-------|----------------------------------------|--|

| Α | В     | $\mathbf{Y} = \mathbf{A} + \mathbf{B}$ |  |

| 0 | 0     | 0                                      |  |

| 0 | 1     | 1                                      |  |

| 1 | 0     | 1                                      |  |

| 1 | 1     | 1                                      |  |

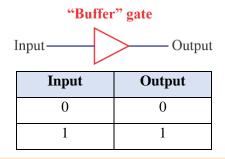

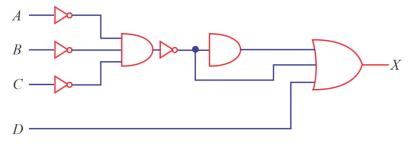

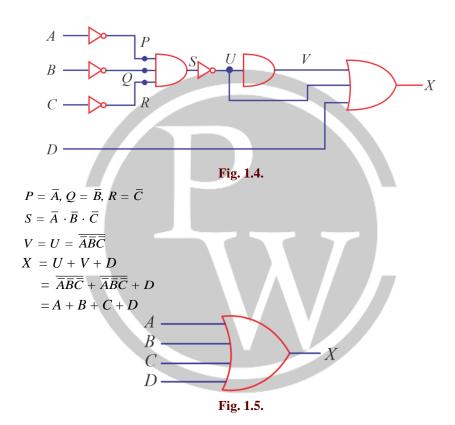

**Example:** Reduce the combinational logic circuit shown figure such that the desired output can be obtained using only one gate.

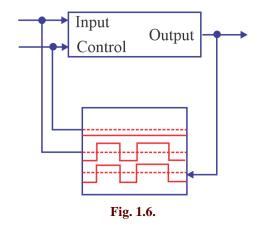

#### Enable:

- Allow a signal to pass when the control signal is HIGH.

- Prevent a signal from passing when the control signal is LOW.

#### **Disable:**

- Prevent a signal from passing when the control signal is HIGH.

- Allow a signal to pass when the control signal is LOW.

- Enable and Disable Functions:

- AND and OR gates can both be used to enable or disable a transmitted waveform.

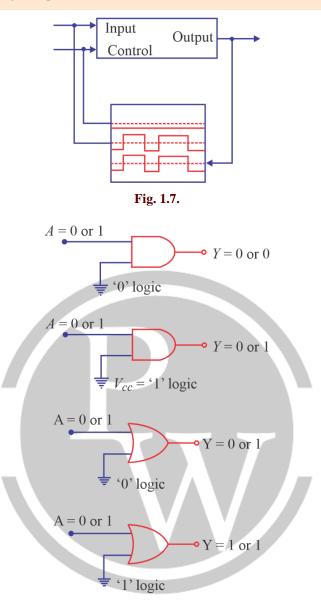

#### For a two input AND gate:

#### For a two input OR gate:

• Control '0' disable

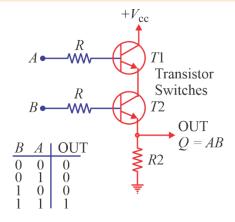

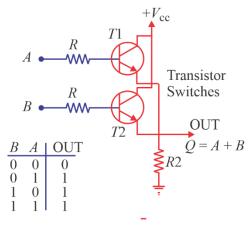

#### **1.1.4.** Switch Diagram for AND/OR gate

#### **1.1.5.** Basic law applications in AND/OR gate.

#### (a) Commutative Law:

The commutative law allows change in position of AND or OR variables. There are two commutative laws.

$$A + B = B + A$$

$$A \times B = B \times A$$

(b) Associative Law:

$$(A+B)+C = A+(B+C)$$

$(A \times B) \times C = A \times (B \times C)$

#### GATE WALLAH COMPUTER SCIENCE & INFORMATION TECHNOLOGY HANDBOOK

#### 1.1.6. Circuit Diagram for AND/OR gate.

## 1.1.7. Switch Diagram for AND/OR Gate

|     | 2 | A'  |       | 1      | A      | Output |

|-----|---|-----|-------|--------|--------|--------|

| NOT |   | A Ā |       | 0<br>1 |        | 1<br>0 |

|     |   |     |       | А      | В      | Output |

|     |   |     | A.B   | 0<br>0 | 0<br>1 | 0<br>0 |

| AND |   |     |       | 1      | 0      | 0      |

|     |   |     |       | 1      | 1      | 1      |

|     |   |     |       | А      | В      | Output |

| OR  |   |     | A + B | 0      | 0      | 0      |

|     |   |     |       | 0      | 1      | 1<br>1 |

|     |   |     |       | 1      | 01     | 1      |

|     |   |     |       | 1      | 1      | 1      |

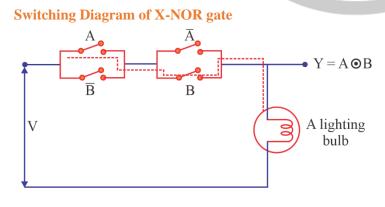

# **1.2. Logic Gates**

Logic gates are the fundamental building blocks of digital systems.

Types of logic gates: There are three basic logic gates, namely

- OR gate

- AND gate

- NOT gate

And other logic gates that are derived from these basic gates are:

- NAND gate

- NOR gate

- Exclusive OR gate

- Exclusive NOR gate

#### **1.2.1. NAND gate:**

The term NAND gate equivalent to AND gate followed by a NOT gate, implies NOT-AND

#### Symbol:

Truth table of 2-input NAND gate.

| ĺ | Input |   | Output              |

|---|-------|---|---------------------|

|   | A     | В | $Y = \overline{AB}$ |

|   | 0     | 0 | 1                   |

|   | 0     | 1 | 1                   |

|   | 1     | 0 | 1                   |

|   | 1     | 1 | 0                   |

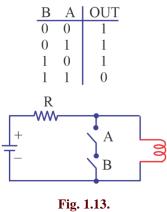

Switching and Circuit Diagram for NAND gate.

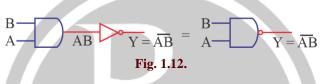

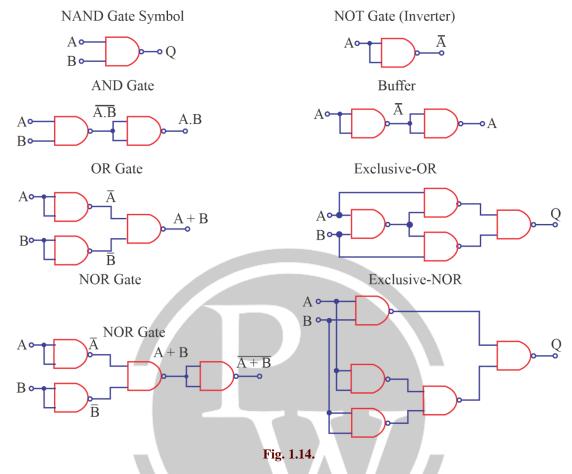

#### NAND gate acts as Universal Gate

#### Logic Gates using only NAND Gates

All the logic gate functions can be created using only NAND gates. Therefore, it is also known as a Universal logic gate.

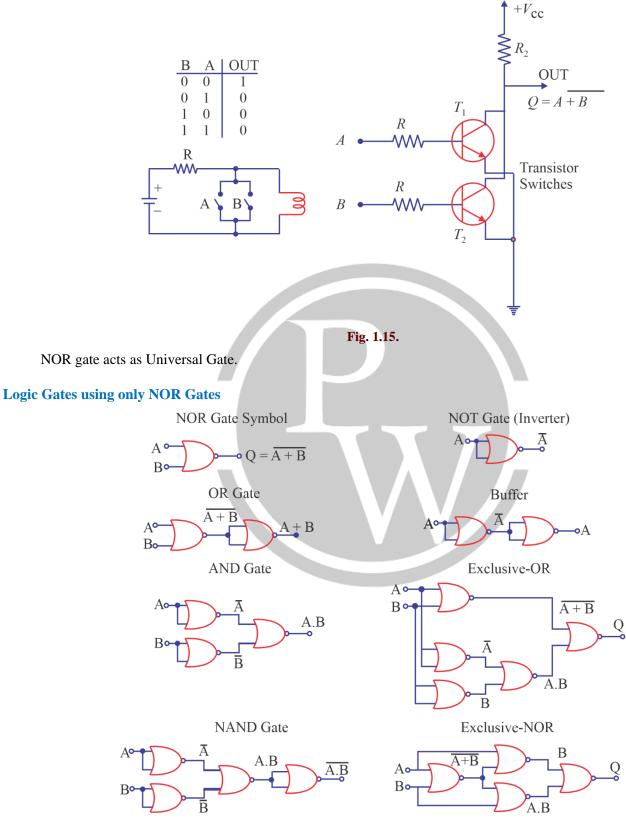

#### 1.2.2. NOR Gate

A NOR gate is equivalent to OR gate followed by a NOT gate.

Symbol:

$$A \xrightarrow{A+B} y = \overline{A+B} = A \xrightarrow{y = \overline{A+B}} B \xrightarrow{y = \overline{A+B}} B$$

#### **Truth Table for 2-input NOR gate**

|   | Input | Output                 |

|---|-------|------------------------|

| Α | В     | $Y = \overline{A + B}$ |

| 0 | 0     | 1                      |

| 0 | 1     | 0                      |

| 1 | 0     | 0                      |

| 1 | 1     | 0                      |

#### Switching and Circuit Diagram for NOR gate

Fig. 1.16.

All the logic gate functions can be created using only NOR gates. Therefore, it is also known as a Universal logic gate.

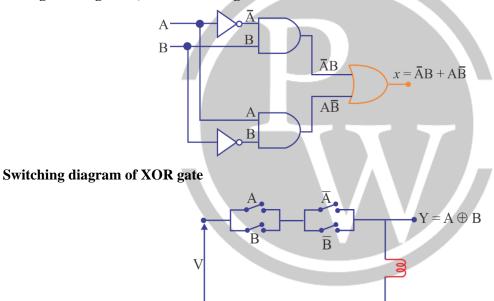

#### 1.2.3. XOR Gate

Symbol of two input XOR gate

$Y = A \oplus B$ B

Truth table for 2-input XOR gate

| ]   | nput | Output                                         |

|-----|------|------------------------------------------------|

| A B |      | $\mathbf{Y} = \mathbf{A} \bigoplus \mathbf{B}$ |

| 0   | 0    | 0                                              |

| 0   | 1    | 1                                              |

| 1   | 0    | 1                                              |

| 1 1 |      | 0                                              |

XOR gate using AND, OR and NOT gate

**Truth Table:**

| Α | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

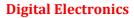

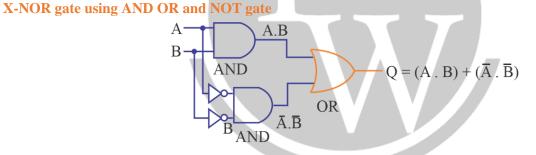

#### 1.2.4. X-NOR gate:

#### Symbol for two input X-NOR gate

Truth table for 2-input X-NOR gate

| I   | nput | Output                                        |  |

|-----|------|-----------------------------------------------|--|

| A B |      | $\mathbf{Y} = \mathbf{A} \bigodot \mathbf{B}$ |  |

| 0   | 0    | 1                                             |  |

| 0   | 1    | 0                                             |  |

| 1   | 0    | 0                                             |  |

| 1   | 1    | 1                                             |  |

Boolean expression for EX-NOR gate is  $Y = \overline{A \oplus B}$

**Apply De-Morgan's theorem:**

$$\overline{A \oplus B} = \overline{\overline{AB} + A\overline{B}} = \overline{\overline{AB}} \cdot \overline{\overline{AB}} = \left(A + \overline{B}\right)\left(\overline{A} + B\right) = AB + \overline{AB}$$

The output of a two input EX-NOR gate is logic '1' when the inputs are same and a logic '0' when they are different.

**Truth Table:**

| Α | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$Y = (A + \overline{B}) (\overline{A} + \overline{B})$$

$$= AB + \overline{A}\overline{B}$$

$$= A \oplus B$$

# 1.3. Alternate Logic Gate Representation

**Example:** In the following circuit, the find the output Z?

Solution: From the given circuit, we can observe that input to last XNOR is same, so, the

XNOR output is given by (let input is X)

$Z = X \cdot X + \overline{X} \cdot \overline{X} = X + \overline{X} = I$

i.e. the output will be high [logic 1] irrespective of the inputs A and B.

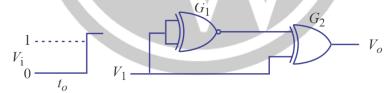

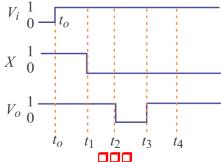

**Example:** The gate  $G_1$  and  $G_2$  in figure shown below have propagation delays of 10ns and 20ns respectively.

If input  $V_i$  makes an abrupt change from logic 0 to 1 at  $t = t_0$ , then find the output waveform  $V_0$ ? Here,  $t_1 = t_0 + 10$  ns,  $t_2 = t_1 + 10$ ns,  $t_3 = t_2 + 10$  ns.

**Solution:** Let the output of  $G_1 = X$

The output waveform will be as shown in figure below.

# MINIMIZATION OF BOOLEAN FUNCTION

# 2.1. Boolean Algebra

Boolean algebra is a system of mathematical logic. It is an algebraic system consisting on the set of elements (0, 1) two binary operators called OR, AND and one unary operator NOT. It is the basic mathematical tools in the analysis and the synthesis of switching circuits. It is a way to express logic functions algebraically.

**Note:** Any functional relation in Boolean algebra can be provided by the method of perfect induction perfect inductions the method of proof, where by a function relation is verified for every possible combination of values that the value may assume.

#### **Axioms of Boolean Algebra:**

Axioms of Boolean algebra are a set of logical expressions that we accept without proof and upon which we can build a set of useful theorem.

|           | AND operator | OR operator | NOT operators      |

|-----------|--------------|-------------|--------------------|

| Axioms 1: | 0.0 = 0      | 0 + 0 = 0   | $\overline{1} = 0$ |

| Axioms 2: | 0.1 = 0      | 0 + 1 = 1   | $\overline{0} = 1$ |

| Axioms 3: | 1.0 = 0      | 1 + 0 = 1   |                    |

| Axioms 4: | 1.1 = 1      | 1 + 1 = 1   |                    |

**Logic operations:** In Boolean Algebra all the algebraic function performed is logical. These actually represents logic operations. The AND, OR and NOT are the basic operations that are performed in Boolean Algebra. In addition to these operations, there are some derived operations such as NAND, NOR, EX-OR and EX-NOR that are also performed in Boolean Algebra.

#### 1.1.1. NOT Operation

The NOT operation in Boolean algebra is similar to inversion in ordinary algebra

$1:\overline{0} = 1$

$2:\overline{1}=0$

3 : if A = 0 then  $\overline{A} = 1$

4 :  $\overline{\overline{A}} = A$  (Double inversion)

#### **1.1.2. AND Operation**

It is a logical operation that are performed by AND gate. The AND operation in Boolean Algebra is similar to multiplication in ordinary algebra.

1:  $\mathbf{A} \cdot \mathbf{0} = \mathbf{0}$  (Null Law)

2:  $\mathbf{A} \cdot \mathbf{1} = \mathbf{A}$  (Identity law)

- 3:  $\mathbf{A} \cdot \mathbf{A} = \mathbf{A}$

- 4:  $\mathbf{A} \cdot \overline{\mathbf{A}} = \mathbf{0}$

#### 1.1.3. OR Operation

It is the logical operation that are performed by OR gate. The OR operation in Boolean Algebra is similar to addition in ordinary algebra.

1: A + 0 = A (Null law) 2: A + 1 = 1 (Identity law) 3: A + A = A 4: A +  $\overline{A}$  = 1

#### **1.1.4. NAND Operation:**

The NAND operation in Boolean Algebra is performed by AND operation followed by NOT operation i.e., the negation of AND operation is performed by NAND gate.

#### **1.1.5. NOR Operation:**

The NOR operation in Boolean Algebra is performed by OR operation followed by NOT operation i.e., the negation of OR operation is performed by NOR gate.

## 2.2. Laws of Boolean Algebra

#### 2.2.1. Commutative Law

$$1. \qquad \mathbf{A} + \mathbf{B} = \mathbf{B} + \mathbf{A}$$

$$A + B + C = B + C + A = C + A + B = B + A + C$$

$2. \qquad AB = BA$

```

A \cdot BC = B \cdot CA = C \cdot AB = B \cdot AC

```

**Violation:** Inhibition (1) for Example x/y (x but not y) is not commutative law it means  $x/y \neq y/x$

#### 2.2.2. Associative law:

This law arrows grouping of variables

- 1. (A + B) + C = A + (B + C)A + (B + C + D) = (A + B + C) + D= (A + B) + (C + D)

- 2.  $(\mathbf{A} \cdot \mathbf{B})\mathbf{C} = \mathbf{A} \cdot (\mathbf{B} \cdot \mathbf{C})$

$A (BCD) = (ABC) \cdot D$

$A (BCD) = AB \cdot CD$

Note:- NAND and NOR gates are not Associative

#### 2.2.3. Distributive Law

1: A(B+C) = AB + AC

$\mathbf{A} + \mathbf{B}\mathbf{C} = (\mathbf{A} + \mathbf{B}) (\mathbf{A} + \mathbf{C})$

#### 2.2.4. Redundant Literal Rule

- 1.  $A + \overline{A}B = A + B$

- 2.  $A(\overline{A} + B) = AB$

#### 2.2.5. Idempotent Law

- 1.  $A \cdot A = A$

- $2. \qquad A + A = A$

#### 2.2.6. Absorption Law

- 1. A + AB = A

- $2. \qquad A(A+B) = A$

#### 2.2.7. Involutionary Law

The law that for any variable A.

$$\overline{A} = (A')' = A$$

#### 2.2.8. Consensus theorem:

There are two consensus theorems

$AB + \overline{A}C + BC = AB + \overline{A}C$

$$(A+B)(\overline{A}+C)(B+C) = (A+B)(\overline{A}+C)$$

## 2.3. De-Morgan's theorem:

De-Morgan's theorem represents two of the most important rules of Boolean algebra.

- $I. \ \overline{A.B} = \overline{A} + \overline{B}$

- II.  $\overline{\mathbf{A} + \mathbf{B}} = \overline{\mathbf{A}} \cdot \overline{\mathbf{B}}$

The above two laws can be extended for 'n' variables as,

$\overline{A_1.A_2.A_3...+A_n} = \overline{A_1} + \overline{A_2} + ...\overline{A_n}$  and  $\overline{A_1 + A_2} + ...+A_n = \overline{A_1.A_2...A_n}$

#### 2.3.1 Duality theorem:

Duality Theorem states that,

- (a) Change each OR sign by an AND sign and vice versa.

- (b) Compliment any '0' or '1' appearing in expression

- (c) Keep literals as it is.

**Note:** With n variables, maximum possible distinct logic function =  $2^{2^n}$

**Example :** If a function is given as  $f = AB + \overline{A}\overline{B}$  then find its complement.

**Solution :** Given  $f = (AB + \overline{A}\overline{B})$

Complement of  $\overline{\mathbf{f}} = \overline{\mathbf{AB} + \overline{\mathbf{A}}\overline{\mathbf{B}}} = \overline{\mathbf{AB}} \cdot \overline{\overline{\mathbf{A}}\overline{\mathbf{B}}}$  $= (\overline{\mathbf{A}} + \overline{\mathbf{B}})(\mathbf{A} + \mathbf{B})$  $= \mathbf{A}\overline{\mathbf{A}} + \mathbf{A}\overline{\mathbf{B}} + \mathbf{B}\overline{\mathbf{A}} + \mathbf{B}\overline{\mathbf{B}} = \mathbf{A}\overline{\mathbf{B}} + \overline{\mathbf{A}}\mathbf{B}$

**Example :** Show that

$AB + B\overline{C} + AC = AC + B\overline{C}$ Solution : LHS = AB + B\overline{C} + AC = AB(C + \overline{C}) + B\overline{C}(A + \overline{A}) + A(B + \overline{B})C = ABC + AB\overline{C} + AB\overline{C} + \overline{A}B\overline{C} + ABC + A\overline{C} + ABC + A\overline{C} + ABC + A\overline{C} + ABC + A\overline{C} + AB\overline{C} + A\overline{B}C + A\overline{C} + A\overline{B}C + A\overline{B}C + A\overline{B}C + A\overline{B}C + A\overline{B}C + A\overline{C}C + A\overline{B}C + A\

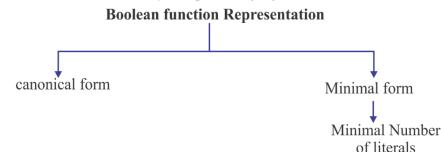

# 2.4. Minimization of Boolean function:

Every Boolean function expression must be reduced to as simple form as possible before realization because every logic operation in the expression represents a corresponding elements of hardware. Realization of digital circuit with minimal expression has several advantages as:

- 1. The number of logic gates will reduced.

- 2. The speed of operation will increase

- 3. power dissipation will decrease

- 4. The FAN IN may reduced

- 5. The complexing of the circuit reduces

The simple method of minimization of Boolean function using certain Algebraic rules which results in the reduction of number of term and/or number of arithmetic operations the various theorem and rules that are already discussed are very useful for the simplification of Boolean expression.

A function of n Boolean variables denoted by  $f(A_1, A_2..., A_n)$  is another variable of Algebra and takes one of the two possible values either 0 or 1. The various way of representing a given function are discussed below.

All the terms contain all the variable either in complementary or in uncomplimentary form

The literal means the Binary variable either in complementary or in uncomplimentary form.

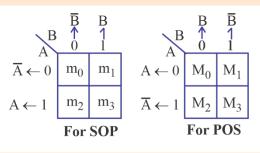

#### 2.4.1. Minimization of Boolean function using k-map

- Using K-map: The Boolean function can be simplified Algebraically but being not a symmetric method, we can never be sure that whether the minimal expression obtained is the real minimal or not.

- **Karnaugh Map (k-map):** A k-map is a graphical representation of Boolean expression, A two variable k-map will have four cell or squares 3-variable k-map will have 8-cells, n-variable k-map will have 2<sup>n</sup> cells.

**Note:** Adjacent cells differ by 1 bit to maintain adjacently property gray code sequence is used in k-maps (Any two adjacent cells will differ by only one bit)

#### Min terms & Max terms:

- 1. n-binary variable have 2<sup>n</sup> possible combinations.

- 2. Min term is a product term, it contains all the variables either complementary or un complementary form for that combination the function output must be '1'.

- Max term is a sum term, it contains all the variables either complementary or uncomplimentary form for that combination the function output must be '0'.

For two variable

| X | У | Min terms                           | Max terms                           |

|---|---|-------------------------------------|-------------------------------------|

| 0 | 0 | $m_0 = \overline{x} \ \overline{y}$ | $M_0 = x + y$                       |

| 0 | 1 | $m_1 = \overline{x} y$              | $M_1 = x + \overline{y}$            |

| 1 | 0 | $m_2 = x \overline{y}$              | $M_2 = \overline{x} + y$            |

| 1 | 1 | $m_3 = x y$                         | $M_3 = \overline{x} + \overline{y}$ |

- In min terms we assigns '1' to each uncomplemented variables and '0' to each complemented variable.

- In Max terms we assign '0' to each uncomplemented variable and '1' to each complemented variables.

## 2.5. Representation of Boolean Functions

Any Boolean expression can be expressed in two forms

- Sum of Product form (SOP)

- Product of Sum form (POS)

#### 2.5.1. SOP Form

The SOP expression usually takes the forms of two or more variables OR together.

$$Y = \overline{A}BC + A\overline{B} + AC$$

$$Y = A\overline{B} + B\overline{C}$$

SOP forms are used to write logical expression for the output becoming logic '1'.

| Inp | Input (3-variables) |   | Output (Y) |

|-----|---------------------|---|------------|

| Α   | В                   | С | Y          |

| 0   | 0                   | 0 | 0          |

| 0   | 0                   | 1 | 0          |

| 0   | 1                   | 0 | 0          |

| 0   | 1                   | 1 | 1          |

| 1   | 0                   | 0 | 0          |

| 1   | 0                   | 1 | 1          |

| 1   | 1                   | 0 | 1          |

| 1   | 1                   | 1 | 1          |

: Notation of SOP expression is:

$f(A, B, C) = \Sigma m(3, 5, 6, 7)$

$Y = m_3 + m_5 + m_6 + m_7$

Also,  $Y = \overline{ABC} + A\overline{BC} + A\overline{BC} + A\overline{BC}$

#### 2.5.2. POS Form

The POS expression usually takes the form of two or more OR variables within parentheses, ANDed with two or more such terms.

**Example:**  $Y = (A + \overline{B} + C)(B\overline{C} + D)$

Each individual term in standard POS form is called maxterm.

POS forms are used to write logical expression for output be coming logic '0'.

we get  $f(A, B, C) = \pi M(0, 1, 2, 4)$

$$Y = M_0.M_1.M_2.M_4$$

$$Y = (\mathbf{A} + \mathbf{B} + \mathbf{C})(\mathbf{A} + \mathbf{B} + \overline{\mathbf{C}})(\mathbf{A} + \overline{\mathbf{B}} + \mathbf{C})(\overline{\mathbf{A}} + \mathbf{B} + \mathbf{C})$$

: We can also conclude from Table 2 and from above equations:

if  $Y = \Sigma m(3, 5, 6, 7)$  or  $Y = \pi M(0, 1, 2, 4)$

# 2.6. Karnaugh Map (K-MAP)

The K-map is a graphical method which provides a systematic method for simplifying the Boolean expressions. In n variable K-map, there are  $2^n$  cells.

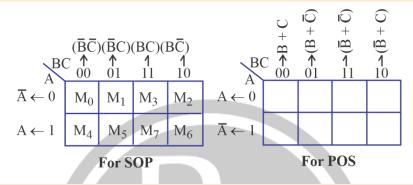

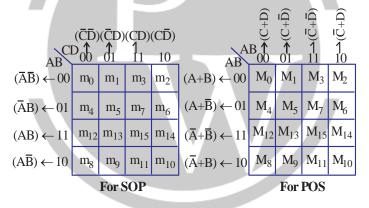

#### 2.6.1. Two variable K-map

#### 2.6.2. Three variable K-map

#### 2.6.3. Four Variable K-map

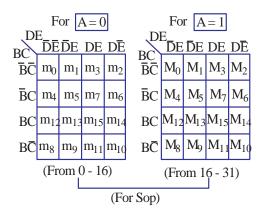

#### 2.6.4. Five variable K-map

• 32 cells

• 32 Minterms (Maxterms)

Here, we have *f*(A, B, C, D, E)

# 2.7. Simplification Rules

- 1. Construct the K-map and place 1's in those cells corresponding to the 1's in the truth table. Place the 0's in the other cells.

- 2. Examine the map for adjacent 1's and loop those 1's which are not adjacent to any other 1's. These are called isolated 1's.

- 3. Next, look for those 1's which are adjacent to only one other 1. Loop any pair containing such a 1.

- 4. Loop any octet even if it contains some 1's that have already been looped.

- 5. Loop any quad that contains one or more 1's which have not already been looped, making sure to use the minimum number of loops.

- 6. Form the OR sum of all the terms generated by each loop.

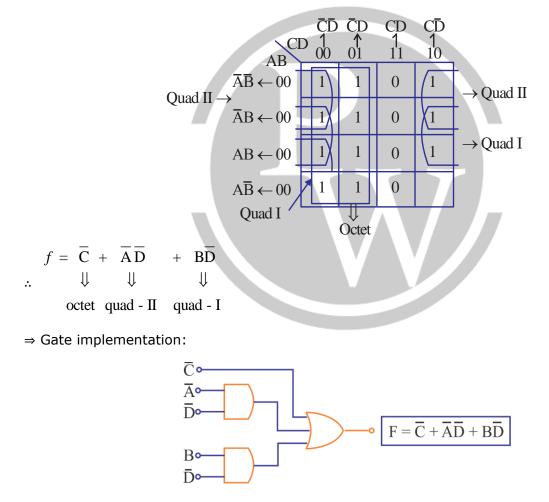

Example: Simply a four variable logic function using K-map

$f(A, B, C, D) = \Sigma m(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$  also implement the simplified expression with AND-OR logic. Solution:

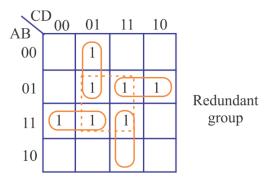

# 2.8. Redundant Group

If all the 1's in a group are already involved in some other groups, then that group is caused as a redundant group. A redundant group has to be eliminated, because it increases the no of gates required.

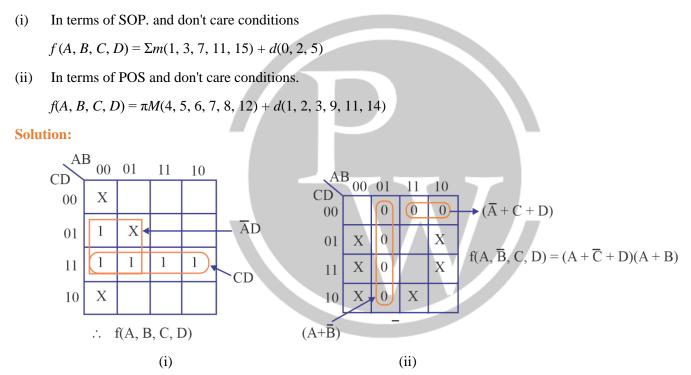

# 2.9. Don't Care Condition

The combinations for which the values of the expression are not specified are called don't care conditions.

**Example:** Simply the given equation in part (i) and (ii)

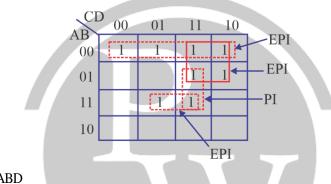

# 2.10. Implicants, Prime Implicants and Essential Prime Implicants

#### 2.10.1. Implicants

Implicants is a product term on the given function for that combination the function output must be 1.

#### 2.10.2. Prime Implicant (PI)

Prime implicant is a smallest possible product term of the given function,

#### 2.10.3. Essential Prime Implicants (EPI)

EPI is a prime implicant it must cover at least one minterms, which is not covered by other PI.

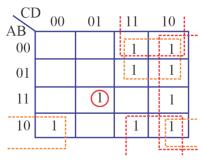

# **Example:** Reduce the expression using mapping $F = \Sigma m(2, 3, 6, 7, 8, 10, 11, 13, 14)$ Solution :

$F = AB\overline{C}D + A\overline{B}\overline{D} + \overline{A}C + \overline{B}C + C\overline{D}$

**Example :** Reduce the following expression using k-map and identify PI's and EPI

$F = \Sigma m(0, 1, 2, 3, 6, 7, 13, 15)$

**Solution :**

$EPI = \overline{A}\overline{B}, \ \overline{A}C, \ ABD$

PI = BCD

Minimal

$$F = \overline{A}\overline{B} + \overline{A}C + ABD$$

**Example:** Given the following Karnaugh map, which one of the following represents the minimal sum of products of the map.

A.  $xy + \overline{y}z$ B.  $\omega \overline{x} \ \overline{y} + xy + xz$ C.  $\overline{\omega}x + \overline{y} \ z + xy$ D. xy + y

| vz    | ° 00 | 01 | 11 | 10 |

|-------|------|----|----|----|

| yz 00 | 0    | х  | 0  | х  |

| 01    | X    | х  | Х  |    |

| 11    | 0    | X  | 1  | 0  |

| 10    | 0    | 1  | Х  | 0  |

$= xy + \overline{y} z$

| yz | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| 00 | 0  | х  | 0  | х  |

| 01 | Х  | х  | Х  | 1  |

| 11 | 0  | х  | 1  | 0  |

| 10 | 0  | 1  | х  | 0  |

mr

# **COMBINATIONAL CIRCUITS**

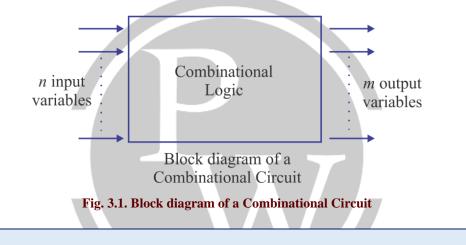

# 3.1. Combinational Circuits

The combinational circuit has 'n' input variables and 'm' output variables. Since, the number of input variables is n, there are  $2^n$  possible combinations of bits at the input. Each output can be expressed in terms of input variables by a Boolean expression.

# 3.2. Adders

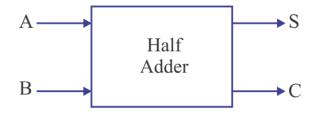

The most basic arithmetic operation is the addition of two binary digits. A combinational circuit that performs the addition of two 1-bit numbers is called as half adder, and the logic circuit that adds three 1-bit numbers is called as full adder.

#### 3.2.1. Half Adder

The logic circuit that performs the addition of two 1-bit numbers is called as half adder. It is the basic building block for addition of two single bit numbers. This circuit has two outputs namely carry (C) and sum (S).

Fig. 3.2. Block Diagram of a 2-bit Half Adder

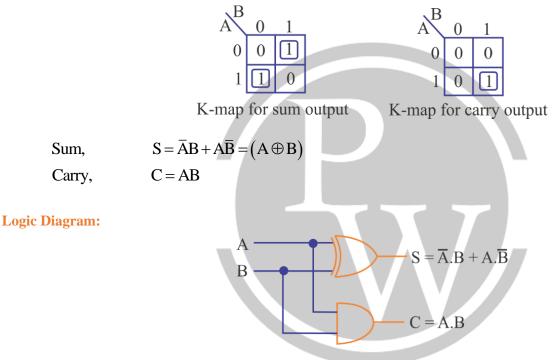

The truth table of half adder: where A and B are the inputs and sum and carry

| Inputs |   | Outputs |           |

|--------|---|---------|-----------|

| А      | В | Sum (S) | Carry (C) |

| 0      | 0 | 0       | 0         |

| 0      | 1 | 1       | 0         |

| 1      | 0 | 1       | 0         |

| 1      | 1 | 0       | 1         |

K-map simplification for Carry and Sum: Boolean expressions for the sum (S) and carry (C) outputs from K – maps:

#### Fig. 3.3. Logic Diagram of Half Adder

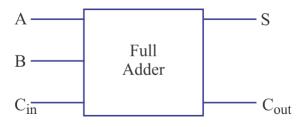

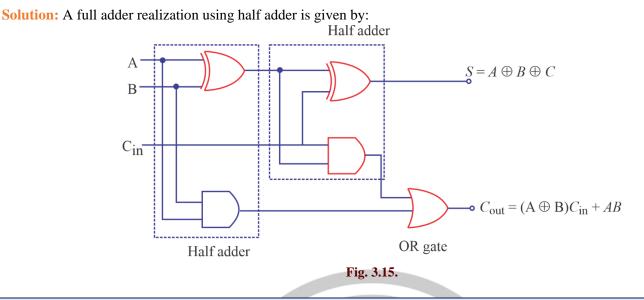

#### 3.2.2. Full Adder

A full adder circuit is an arithmetic circuit block that can be used to add three bits to produce a sum and a carry output. Let us consider A and B as two 1-bit inputs &  $C_{in}$  is a carry generated from the previous order bit additions. Let S (sum) and  $C_{out}$  (carry) are the outputs of the full adder.

Fig. 3.4. Block Diagram of a Full Adder

#### The Truth Table for Full Adder is given as:

| Inputs |   |                 | Outp    | outs       |

|--------|---|-----------------|---------|------------|

| Α      | В | C <sub>in</sub> | Sum (S) | Carry Cout |

| 0      | 0 | 0               | 0       | 0          |

| 0      | 0 | 1               | 1       | 0          |

| 0      | 1 | 0               | 1       | 0          |

| 0      | 1 | 1               | 0       | 1          |

| 1      | 0 | 0               | 1       | 0          |

| 1      | 0 | 1               | 0       | 1          |

| 1      | 1 | 0               | 0       | 1          |

| 1      | 1 | 1               | 1       | 1          |

#### Table: Truth Table for Full Adder

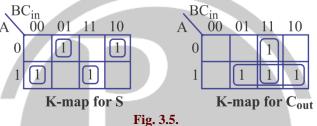

#### **K** – map Simplification for Carry and Sum:

Simplified Boolean expressions for the sum (S) and carry (Cout) output from K-maps is

$\begin{array}{ll} \text{Sum,} & S = \overline{A}\overline{B}C_{\text{in}} + \overline{A}B\overline{C}_{\text{in}} + ABC_{\text{in}} + A\overline{B}\overline{C}_{\text{in}} = C_{\text{in}}\left(\overline{A}\overline{B} + AB\right) + \overline{C}_{\text{in}}\left(\overline{A}B + A\overline{B}\right) \\ & = C_{\text{in}}\left(A \odot B\right) + C_{\text{in}}\left(A \oplus B\right) \\ & = C_{\text{in}}\left(\overline{A \oplus B}\right) + C_{\text{in}}\left(A \oplus B\right) \\ \text{Sum,} & S = C_{\text{in}} \oplus A \oplus B \\ \text{Carry,} & C_{\text{out}} = AB + AC_{\text{in}} + BC_{\text{in}} \end{array}$

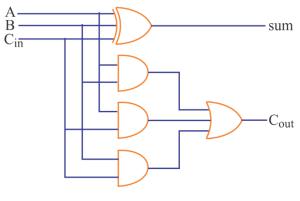

#### Logic Diagram:

We can realize logic diagram of a full adder using gates as shown in below figure:

Fig. 3.6. Logic Diagram of Full Adder

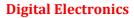

**Example:** A full adder is implemented using two input OR gate and two half adders. Half adder is implemented using two input XOR and two input AND gate. The propagation delays of XOR gate, AND gate and OR gate respectively are 2ns, 1.5ns. and 1ns. The propagation delay of full adder is .... ns.

#### **Solution:**

Fig. 3.7.

# 3.3. Subtractors

#### 3.3.1. Half subtractor

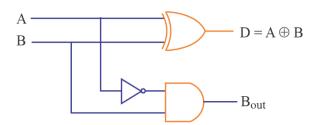

A half subtractor is a combinational logic circuit, which performs the subtraction of two 1-bit numbers. It subtracts one binary digit from another to produce a DIFFERENCE output and a BORROW output.

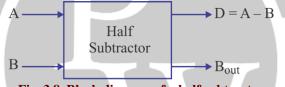

Fig. 3.8. Block diagram of a half subtractor

The truth table of half – subtractor, where A, B are the inputs, and difference (D) and borrow (B) are the outputs.

Table: Truth table of Half – Subtractor

| Inputs |   | Outp | outs |

|--------|---|------|------|

| Α      | В | D    | Bout |

| 0      | 0 | 0    | 0    |

| 0      | 1 | 1    | 1    |

| 1      | 0 | 1    | 0    |

| 1      | 1 | 0    | 0    |

#### **K** – map Simplification for Difference and Borrow:

K-map for diffrence output

K-map for borrow output

Difference,

Borrow,

$\mathbf{B}_{out} = \overline{\mathbf{A}}\mathbf{B}$

$D = \overline{A}B + A\overline{B} = A \oplus B$

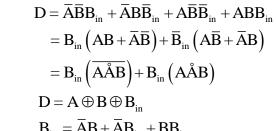

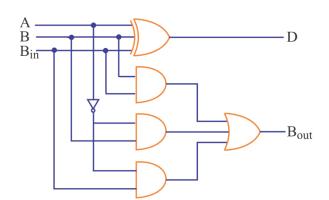

#### 3.3.2. Full Subtractor

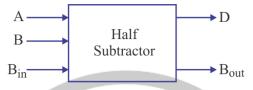

A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend.

Fig. 3.10. Block Diagram of a Full subtractor

#### **Truth table of Full subtractor:**

| ble: Truth ta | ble of Full | subtractor |

|---------------|-------------|------------|

|---------------|-------------|------------|

| - |        | _   |   |      |  |

|---|--------|-----|---|------|--|

| Ι | Inputs |     |   | puts |  |

| Α | В      | Bin | D | Bout |  |

| 0 | 0      | 0   | 0 | 0    |  |

| 0 | 0      | 1   | 1 | 1    |  |

| 0 | 1      | 0   | 1 | 1    |  |

| 0 | 1      | 1   | 0 | 1    |  |

| 1 | 0      | 0   | 1 | 0    |  |

| 1 | 0      | 1   | 0 | 0    |  |

| 1 | 1      | 0   | 0 | 0    |  |

| 1 | 1      | 1   | 1 | 1    |  |

#### K – map simplification for Difference and Borrow:

K-map for borrow output

K-map for difference output

Difference,

Fig. 3.11. Logic Diagram of a Full Subtractor

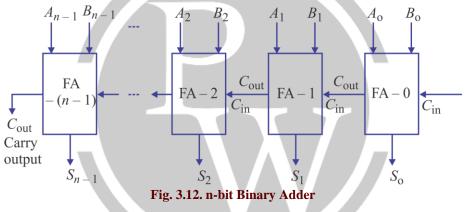

# 3.4. Binary Parallel Adder

An n-bit parallel adder can be constructed using n number of full adders are connected in parallel and hence; it is also known as parallel adder such that the previous carry or carry input for adder 0 is set to zero. The carry output of each adder is connected to the carry input of the next higher order adder. Hence, it is also known as carry propagate adder.

#### 3.4.1. Propagation Delay in Parallel Adder:

Parallel adders suffer from propagation delay problem because higher bit additions depend on the carry generated from lower bit addition. In effect, carry bits must propagate or ripple through all stages before the most significant sum bit is valid. Thus, the total sum (the parallel output) is not valid until after the cumulative delay of all the adder.

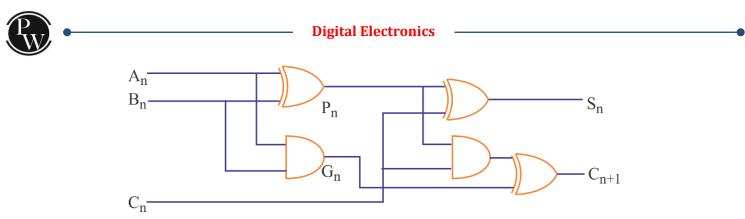

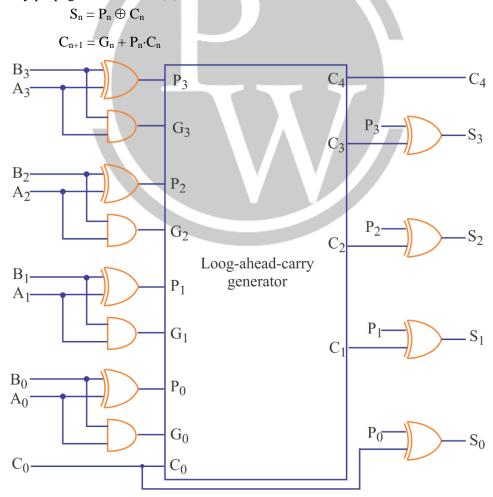

# 3.5. Carry Look Ahead Adder

The look ahead carry adder speeds up the operation by eliminating this ripple carry delay. It examines all the input bits simultaneously and also generates the carry in bits for all the stages simultaneously. The method of speeding up the addition process is based on the two additional functions of the full adder called the carry generate and carry propagate functions.

#### **3.5.1. Carry Generation**

Carry is generated only if both the input bits are 1, that is, if both the bits A and B are 1's, a carry has to be generated in this stage regardless of whether the input carry  $C_{in}$  is a 0 or a 1. Let G as the carry generation function,

$$\mathbf{G} = \mathbf{A} \cdot \mathbf{B}$$

Consider the present bit as the n<sup>th</sup>, then

$$\mathbf{G}_{n} = \mathbf{A}_{n} \cdot \mathbf{B}_{n}$$

Fig. 3.13. Carry Look - ahead Generator Circuit

#### 3.5.2. Carry Propagation

A carry is propagated if any one of the two input bits A or B is 1. If both A and B are 0, a carry will never be propagated. On the other hand, if both A and B are 1, then will not propagate the carry but will generate the carry. Let P as the carry - propagation function, then

$$\mathbf{P}_n = \mathbf{A}_n \oplus \mathbf{B}_n$$

#### 3.5.3. Look ahead Expressions

Let n<sup>th</sup> bit adder, the sum (S) and the carry out (C) for the n<sup>th</sup> bit may be expressed in terms of the carry generation function (G) and the carry propagation function (P) as

Fig. 3.14. 4-bit Full Adder with a look Ahead Carry Generator

**Example:** A full adder can be realized using half adder? Explain it in detail.

# 3.6. Comparator

The comparator is a combinational logic circuit. It compares the magnitude of two n-bit numbers and provides the relative result as the output. Let A and B are the two n-bit inputs. The comparator has three outputs namely A > B, A = B and A < B. Depending upon the result of comparison, one of these outputs will go high.

Fig. 3.16. Block diagram of digital comparator

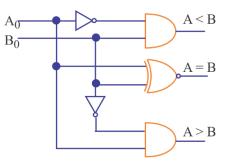

#### 3.6.1. 1-bit Magnitude Comparator

The 1-bit comparator is a combinational logic circuit with two inputs A and B and three outputs namely A < B, A = B and A > B.

| Inputs |   | Outputs   |                                        |          |  |

|--------|---|-----------|----------------------------------------|----------|--|

| Α      | B | X (A < B) | $\mathbf{Y} (\mathbf{A} = \mathbf{B})$ | Z(A > B) |  |

| 0      | 0 | 0         | 1                                      | 0        |  |

| 0      | 1 | 1         | 0                                      | 0        |  |

| 1      | 0 | 0         | 0                                      | 1        |  |

| 1      | 1 | 0         | 1                                      | 0        |  |

Table : Truth Table of a 1-bit Comparator

Design of 1-bit Magnitude Comparator: We can write the expressions for the three outputs as under:

For (A < B),

$$X = \overline{A}_0 B_0$$

For (A = B),  $Y = \overline{A}_0 \overline{B}_0 + A_0 B_0 = \overline{A_0 \oplus B_0}$

For (A > B),  $Z = A_0 \overline{B}_0$

Logic Diagram of 1-bit Comparator:

Fig. 3.17. Logic Diagram of 1-bit Comparator

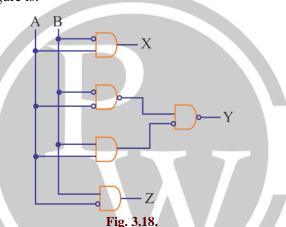

**Example:** The circuit shown in given figure is:

Solution: From the logic circuit shown in the figure, we obtain the following results,

$$X = A\overline{B}$$

$$Y = \overline{(\overline{\overline{A}\overline{B}})(\overline{AB})} = \overline{A}\overline{B} + AB = A \odot B$$

$$Z = \overline{A}B$$

It A > B, then x = 1It It

| t | $\mathbf{A}=\mathbf{B},$ | the  | $\mathbf{y} = \mathbf{I}$ |

|---|--------------------------|------|---------------------------|

| t | A < B,                   | then | z = 1                     |

Therefore, it is a comparator circuit.

# 3.7. Multiplexer

А В Х Υ Ζ 0 0 0 0 1 0 0 1 0 1 1 0 1 0 0 0 1 0 1 1

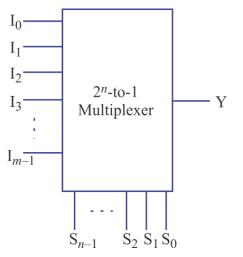

A multiplexer, abbreviated as MUX, is a digital switch which selects one of the many inputs to a single output. A number of control lines determine which input data is to be routed to the output. If there are n select lines, then the number of maximum possible input lines is  $2^n$  and the multiplexer is referred to as a  $2^n$ -to-1 multiplexer or  $2^n \times 1$  multiplexer.

Fig. 3.19. Block diagram of a 2<sup>n</sup> to 1 multiplexer

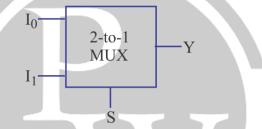

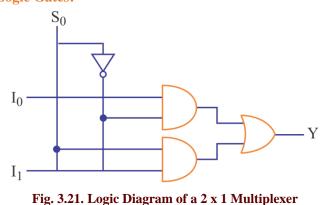

#### 3.7.1. 2 × 1 MUX

A 2 to 1 multiplexer has 2 inputs. Since  $2 = 2^1$ , this multiplexer will have one control (select) line. It has two data inputs I<sub>0</sub> and I<sub>1</sub>, one select input S, and one output.

Fig. 3.20. Schematic block diagram of 2:1 Multiplexer

The truth table of this MUX is given below,

| Select Line<br>(S) | Output<br>Y    |   |

|--------------------|----------------|---|

| 0                  | I <sub>0</sub> | ĺ |

| 1                  | $I_1$          |   |

Thus, the SOP expression for the output Y is,

$$Y = I_0 \overline{S}_0 + I_1 S_0$$

**Realization of a 2:1 MUX using Logic Gates:**

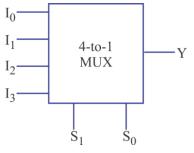

#### 2.7.2. 4 × 1 MUX

A 4-to-1 multiplexer has 4 inputs and two select lines, where  $I_0$  to  $I_3$  are the four inputs to the multiplexer, and  $S_0$  and  $S_1$  are the select lines.

Fig. 3.22. Schematic block diagram of 4 x 1 MUX

#### **Truth Table of a 4-to-1 Multiplexer**

| Select Inputs |       |                | Output         |  |

|---------------|-------|----------------|----------------|--|

|               | $S_1$ | S <sub>0</sub> | Y              |  |

|               | 0     | 0              | Io             |  |

|               | 0     | 1              | I <sub>1</sub> |  |

|               | 1     | 0              | I <sub>2</sub> |  |

|               | 1     | 1              | I <sub>3</sub> |  |

Output Y for a 4-input multiplexer is

$Y = I_0 \bar{S}_1 \bar{S}_0 + I_1 \bar{S}_1 S_0 + I_2 S_1 \bar{S}_0 + I_3 S_1 S_0$

# 3.8. Implementation of Higher Order Mux Using Lower Order MUX

The methods for implementing higher order MUX using lower order MUX are

- **Step 1:** If  $2^n$  is the number of input lines in the available lower order multiplexer and  $2^N$  is the number of input lines in the desired multiplexer, then the number of lower order multiplexers required to construct the desired multiplexer circuit would be  $2^N n$ .

- Step 2: From the knowledge of the number of selection inputs of the available multiplexer and that of the desired multiplexer, connect the less significant bits of the selection inputs of the desired multiplexer to the selection inputs of the available multiplexer.

- **Step 3:** The most significant bits of the selection inputs of the desired multiplexer circuit are used to enable or disable the individual multiplexers so that their outputs when OR produce the final output.

**Example:** In realization of 32 : 1 MUX using 2 : 1 MUX, the required number of 2 : 1 MUX is ?

**Solution:** In realization of  $2^n : 1$  MUX using 2 : 1 MUX, the required number of 2 : 1 MUX is  $2^n - 1$ , since, we have to realize 32 : 1 MUX, so we have

*n* = 5

Hence, the required number of 2 : 1 MUX is

$2^n - 1 = 2^5 - 1 = 31$

# **3.9. Applications of Multiplexers**

- 1. It is used as a data selector to select one out of many data inputs.

- 2. They are used in designing the combinational circuits.

- 3. They are used in digital-to-analog and analog-to-digital converters.

- 4. They can be used for simplification of logic design.

- 5. Multiplexers are also used in data acquisition systems.

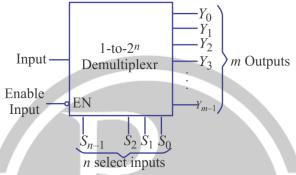

# 3.10. Demultiplexer

The demultiplexer is a combinational logic circuit that performs the reverse operation of a multiplexer. The demultiplexer has one input line and m output lines. Again  $m = 2^n$ , so it requires n select lines. A demultiplexer with one input and m output is called a 1-to-m demultiplexer.

The demultiplexer has one input line and m output lines. Again  $m = 2^n$ , so it requires n select lines. A demultiplexer with one

input and m outputs is called a 1-to-m demultiplexer.

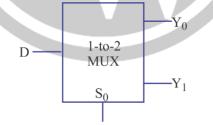

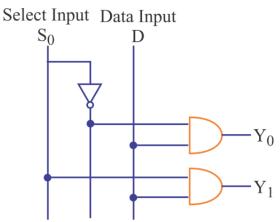

#### 3.10.1. 1 × 2 Demultiplexer

A 1 to 2 demultiplexer has one input and two outputs. Since  $2 = 2 \times 1$ , it requires only one control (select) line.

Fig. 3.24. Logic Diagram of 1 x 2 De-MUX

#### Truth table of a 1-to-2 demultiplexer

Table: Truth table of a 1-to-2 demultiplexer

| Input Select input | Output      |

|--------------------|-------------|

| S S0               | $Y_1 = Y_0$ |

| D 0                | 0 D         |

| D 1                | D 0         |

Thus, the Boolean expressions for the outputs can be written as

```

Y_0 = D\bar{S}_0 \And Y_1 = DS_0

```

# **Realization of a 1 x 2 Demultiplexer using Logic Gates:**

Fig. 3.25. Logic Diagram of 1 × 2 Demultiplexer

# 3.10.2. Applications of Demultiplexers

Demultiplexers are used in

- 1. Data transmission

- 2. Implementation of Boolean Functions

- 3. Combinational logic circuit design

- 4. Generate enable signals (enable one out of many). The application of enable signals in microprocessor systems are:

- (a) Selecting different banks of memory

- (b) Selecting different input/output devices for data transfer

- (c) Enabling different functional units

- (d) Enabling different rows of memory chips depending on address

# 3.11. Comparison Between Multiplexer and Demultiplexer

#### Table : Comparison between Multiplexer and Demultiplexer

| S.No. | Parameter of comparison                              | Multiplexer                   | Demultiplexer                 |

|-------|------------------------------------------------------|-------------------------------|-------------------------------|

| 1.    | Type of logic circuit                                | Combinational                 | Combinational                 |

| 2.    | Number of data inputs                                | m                             | 1                             |

| 3.    | Number of select inputs                              | n                             | Ν                             |

| 4.    | Number of data output                                | 1                             | М                             |

| 5.    | Relation between input/output lines and select lines | $m = 2^n$                     | $M = 2^N$                     |

| 6.    | Operation principle                                  | Many to 1 or as data selector | 1 to many or data distributor |

# 3.12. Decoder

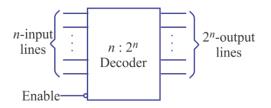

A decoder is a combinational circuit that converts an n-bit binary input data into  $2^n$  output lines, such that each output line will be activated for only one of the possible combinations of inputs. Decoders are usually represented as n-to- $2^n$  line decoders, where n is the number of input lines and  $2^n$  is the number of maximum possible output lines.

#### Fig. 3.26. Block Diagram of n-to-2<sup>n</sup> Decoder

If there are some unused or 'don't care' combinations in the n-bit code, then there will be less than 2n output lines. In general, if n and m are respectively the numbers of input and output lines, then  $m \le 2n$ .

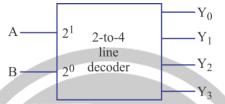

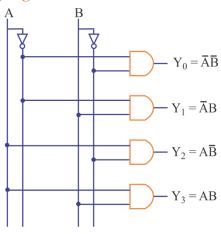

#### 3.12.1. 2 to 4 Line Decoder

Consider a 2 to 4-line decoder, where A and B are two inputs whereas  $Y_0$  through  $Y_3$  are the four outputs.

Fig. 3.27. Block Diagram of a 2 to 4 Line Decoder

**Truth Table of a 2 to 4 Line Decoder**

Table : Truth Table of a 2 to 4 Line Decoder

| Inputs |                | Out                   | puts             |                       |

|--------|----------------|-----------------------|------------------|-----------------------|

| A B    | Y <sub>0</sub> | <b>Y</b> <sub>1</sub> | $\mathbf{Y}_{2}$ | <b>Y</b> <sub>3</sub> |

| 0 0    | 1              | 0                     | 0                | 0                     |

| 0 1    | 0              | 1                     | 0                | 0                     |

| 1 0    | 0              | 0                     | 1                | 0                     |

| 1 1    | 0              | 0                     | 0                | 1                     |

The Boolean expressions for the four outputs is given as:

$$Y_0 = A B$$

and  $Y_1 = AB$

$Y_2 = A\overline{B}$  and  $Y_3 = AB$

**Realization of a 2 to 4 Line Decoder using Logic Gates**

Fig. 3.28. Logic Diagram of a 2 to 4 Line Decoder

#### 3.12.2. Applications of Decoder

Some of important applications of decoder are as follows:

- 1. When the decoder inputs come from a counter which is being continually pulsed, the decoder outputs will be activated sequentially. Hence, they can be used as timing or sequencing signals to turn devices on or off at specific times.

- 2. Decoder are use in memory system of a computer where they respond to the address code generated by the microprocessor to activate a particular memory location.

- 3. They are also used in computers for selection of external devices that include printers, modems, scanners, internal disk drives, keyboard, video monitor etc.

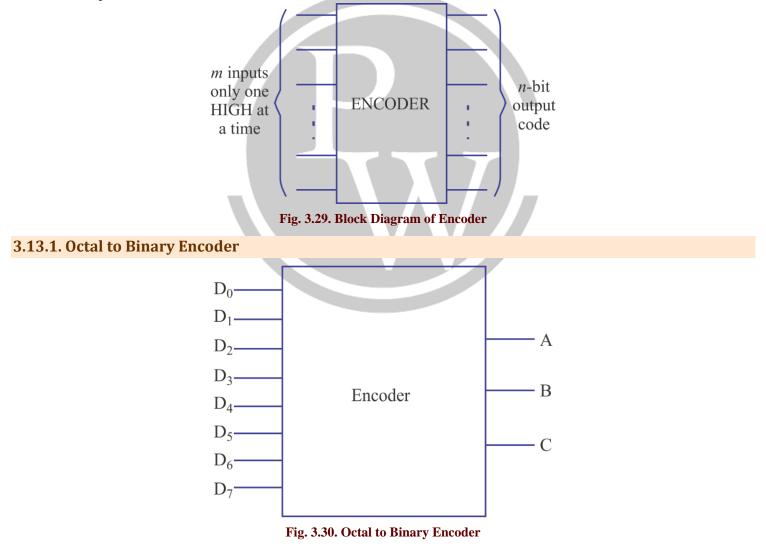

# 3.13. Encoders

An encoder is a combinational logic circuit that performs the inverse operation of a decoder. An encoder has  $2^n$  (or fewer) input lines and n output lines.

# Truth Table of an Octal to Binary Encoder:

Table: Truth Table of an Octal to Binary Encoder

|                  |                |                |                |                |            |                       | <u>.</u>       |   |   |   |

|------------------|----------------|----------------|----------------|----------------|------------|-----------------------|----------------|---|---|---|

|                  |                |                | Outputs        |                |            |                       |                |   |   |   |

| $\mathbf{D}_{0}$ | $\mathbf{D}_1$ | $\mathbf{D}_2$ | $\mathbf{D}_3$ | $\mathbf{D}_4$ | <b>D</b> 5 | <b>D</b> <sub>6</sub> | $\mathbf{D}_7$ | Α | В | С |

| 1                | 0              | 0              | 0              | 0              | 0          | 0                     | 0              | 0 | 0 | 0 |

| 0                | 1              | 0              | 0              | 0              | 0          | 0                     | 0              | 0 | 0 | 1 |

| 0                | 0              | 1              | 0              | 0              | 0          | 0                     | 0              | 0 | 1 | 0 |

| 0                | 0              | 0              | 1              | 0              | 0          | 0                     | 0              | 0 | 1 | 1 |

| 0                | 0              | 0              | 0              | 1              | 0          | 0                     | 0              | 1 | 0 | 0 |

| 0                | 0              | 0              | 0              | 0              | 1          | 0                     | 0              | 1 | 0 | 1 |

| 0                | 0              | 0              | 0              | 0              | 0          | 1                     | 0              | 1 | 1 | 0 |

| 0                | 0              | 0              | 0              | 0              | 0          | 0                     | 1              | 1 | 1 | 1 |

The logical expressions for the outputs as follows:

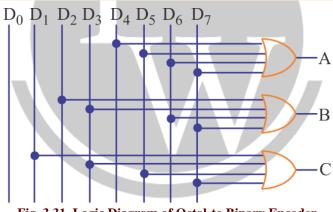

$$\label{eq:alpha} \begin{split} A &= D_4 + D_5 + D_6 + D_7 \\ B &= D_2 + D_3 + D_6 + D_7 \end{split}$$

$D = D_2 + D_3 + D_6 + D_7$  $C = D_1 + D_3 + D_5 + D_7$

$C = D_1 + D_3 + D_5 + D_7$

### 3.13.2. Octal to Binary Encoder

Fig. 3.31. Logic Diagram of Octal-to Binary Encoder

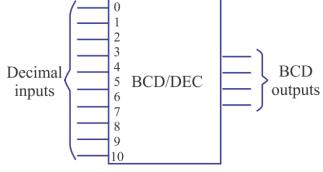

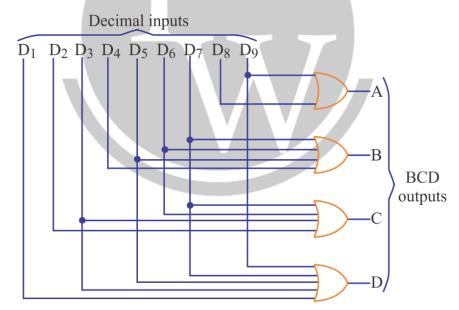

## **3.13.3. Decimal to BCD Encoder**

This type of encoder has 10 inputs one for each decimal digit and 4 outputs corresponding to the BCD code.

Fig. 3.32. Block Diagram of a Decimal-to-BCD Encoder

## **Truth Table of a Decimal to Binary Encoder:**

Table : Truth Table of a Decimal to Binary Encoder

|                | _              | _              | _                     | Inj        |            | _                     | _              | _              | _          |   | Out | tput |   |

|----------------|----------------|----------------|-----------------------|------------|------------|-----------------------|----------------|----------------|------------|---|-----|------|---|

| 0              | 1              | 2              | 3                     | 4          | 5          | 6                     | 7              | 8              | 9          |   | 04  | -p   |   |

| $\mathbf{D}_0$ | $\mathbf{D}_1$ | $\mathbf{D}_2$ | <b>D</b> <sub>3</sub> | <b>D</b> 4 | <b>D</b> 5 | <b>D</b> <sub>6</sub> | $\mathbf{D}_7$ | $\mathbf{D}_8$ | <b>D</b> 9 | Α | В   | С    | D |

| 1              | 0              | 0              | 0                     | 0          | 0          | 0                     | 0              | 0              | 0          | 0 | 0   | 0    | 0 |

| 0              | 1              | 0              | 0                     | 0          | 0          | 0                     | 0              | 0              | 0          | 0 | 0   | 0    | 1 |

| 0              | 0              | 1              | 0                     | 0          | 0          | 0                     | 0              | 0              | 0          | 0 | 0   | 1    | 0 |

| 0              | 0              | 0              | 1                     | 0          | 0          | 0                     | 0              | 0              | 0          | 0 | 0   | 1    | 1 |

| 0              | 0              | 0              | 0                     | 1          | 0          | 0                     | 0              | 0              | 0          | 0 | 1   | 0    | 0 |

| 0              | 0              | 0              | 0                     | 0          | 1          | 0                     | 0              | 0              | 0          | 0 | 1   | 0    | 1 |

| 0              | 0              | 0              | 0                     | 0          | 0          | 1                     | 0              | 0              | 0          | 0 | 1   | 1    | 0 |

| 0              | 0              | 0              | 0                     | 0          | 0          | 0                     | 1              | 0              | 0          | 0 | 1   | 1    | 1 |

| 0              | 0              | 0              | 0                     | 0          | 0          | 0                     | 0              | 1              | 0          | 1 | 0   | 0    | 0 |

| 0              | 0              | 0              | 0                     | 0          | 0          | 0                     | 0              | 0              | 1          | 1 | 0   | 0    | 1 |

Fig. 3.33. Logic Diagram of Decimal-to-BCD encoder

The outputs of a decimal-to-BCD encoder:

$$\begin{split} A &= D_8 + D_9 \\ B &= D_4 + D_5 + D_6 + D_7 \\ C &= D_2 + D_3 + D_6 + D_7 \\ D &= D_1 + D_3 + D_5 + D_7 + D_9 \end{split}$$

# **3.14. Priority Encoder**

## 3.14.1. Truth Table of a Four Input Priority Encoder: (Taking LSB as priority)

#### Table: Truth Table of a Four Input Priority Encoder

|                | Inp            | Out            | puts           |   |   |

|----------------|----------------|----------------|----------------|---|---|

| D <sub>0</sub> | $\mathbf{D}_1$ | $\mathbf{D}_2$ | $\mathbf{D}_3$ | Α | В |

| 0              | 0              | 0              | 0              | Х | Х |

| 1              | 0              | 0              | 0              | 0 | 0 |

| Х              | 1              | 0              | 0              | 0 | 1 |

| Х              | Х              | 1              | 0              | 1 | 0 |

| Х              | Х              | Х              | 1              | 1 | 1 |

According to the truth table, the higher the subscript number, the higher the priority of the input. The X's are don't care conditions indicating that the binary values they represent may be equal to 0 or 1.

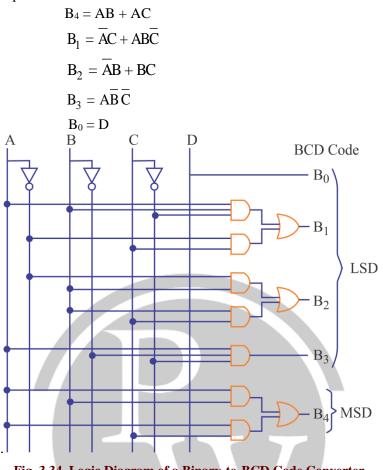

# **3.15. Code Converters**

A code converter is a combinational logic circuit which accepts the input information in one binary code, converts it and produces an output into another binary code.

# 3.15.1. The truth table for 4-bit Binary and its Equivalent BCD

#### Table: Truth table for 4-bit Binary and its Equivalent BCD

| Decimal |   | - | Input |   | BCD Outp              |                       |                       |                       | —              |  |

|---------|---|---|-------|---|-----------------------|-----------------------|-----------------------|-----------------------|----------------|--|

|         | A | B | С     | D | <b>B</b> <sub>4</sub> | <b>B</b> <sub>3</sub> | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | B <sub>0</sub> |  |

| 0       | 0 | 0 | 0     | 0 | 0                     | 0                     | 0                     | 0                     | 0              |  |

| 1       | 0 | 0 | 0     | 1 | 0                     | 0                     | 0                     | 0                     | 1              |  |

| 2       | 0 | 0 | 1     | 0 | 0                     | 0                     | 0                     | 1                     | 0              |  |

| 3       | 0 | 0 | 1     | 1 | 0                     | 0                     | 0                     | 1                     | 1              |  |

| 4       | 0 | 1 | 0     | 0 | 0                     | 0                     | 1                     | 0                     | 0              |  |

| 5       | 0 | 1 | 0     | 1 | 0                     | 0                     | 1                     | 0                     | 1              |  |

| 6       | 0 | 1 | 1     | 0 | 0                     | 0                     | 1                     | 1                     | 0              |  |

| 7       | 0 | 1 | 1     | 1 | 0                     | 0                     | 1                     | 1                     | 1              |  |

| 8       | 1 | 0 | 0     | 0 | 0                     | 1                     | 0                     | 0                     | 0              |  |

| 9       | 1 | 0 | 0     | 1 | 0                     | 1                     | 0                     | 0                     | 1              |  |

| 10      | 1 | 0 | 1     | 0 | 1                     | 0                     | 0                     | 0                     | 0              |  |

| 11      | 1 | 0 | 1     | 1 | 1                     | 0                     | 0                     | 0                     | 1              |  |

| 12      | 1 | 1 | 0     | 0 | 1                     | 0                     | 0                     | 1                     | 0              |  |

| 13      | 1 | 1 | 0     | 1 | 1                     | 0                     | 0                     | 1                     | 1              |  |

| 14      | 1 | 1 | 1     | 0 | 1                     | 0                     | 1                     | 0                     | 0              |  |

| 15      | 1 | 1 | 1     | 1 | 1                     | 0                     | 1                     | 0                     | 1              |  |

The minimized expression of outputs are as follows:

# Fig. 3.34. Logic Diagram of a Binary-to-BCD Code Converter

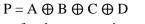

# 3.16. Parity Generator

Parity generators are circuits that accept an (n-1) bit data stream and generate an extra bit that is transmitted with the bit stream. This extra bit is referred to as the parity bit. The parity added in binary message is such that the total number of 1's in the message can be either odd or even according to the type of parity used.

## 3.16.1. Even Parity Generator

The even parity generator is a combinational logic circuit that generates the parity bit such that the number of 1's in the message becomes even. The parity bit is '1' if there are odd number of 1's in the data stream and the parity bit is '0' if there are even number of 1's in the data stream.

#### Truth table for 4-bit data with Even Parity:

|   | 4-bit | data | <b>Even Parity</b> |   |

|---|-------|------|--------------------|---|

| Α | В     | С    | D                  | Р |

| 0 | 0     | 0    | 0                  | 0 |

| 0 | 0     | 0    | 1                  | 1 |

| 0 | 0     | 1    | 0                  | 1 |

| 0 | 0     | 1    | 1                  | 0 |

#### Table: Truth table for 4-bit data with Even Parity

| 0 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

The minimized expression for even parity generator is

The logic diagram for the even parity generator is given as

Fig. 3.35. Logic diagram of even parity generator

## 3.16.2. Odd Parity Generator

· .

The odd parity generator is a combinational logic that generates the parity bit such that the number of 1's in the message becomes odd. The parity bit is '0' for odd number of 1's and '1' for even number of 1's in the bit stream.

Example: A parity generation circuit required to generator on odd parity bit may use ——?

Solution: Odd parity generation circuit consists of combination of EX-OR and EX-NOR gates, whereas even priority generator consists only EX-OR gates.

It is combination of EX-OR and EX-NOR gates.

# SEQUENTIAL LOGIC CIRCUITS

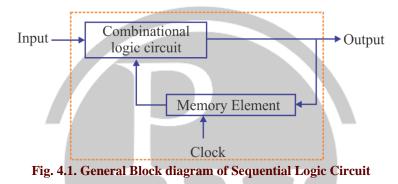

# 4.1. Sequential Logic Circuits

In sequential logic circuits, the output is a function of the present inputs as well as the inputs and outputs. Sequential circuit include memory elements to store past data. The flip-flop is a basic element of sequential logic circuits.

There are two types of sequential circuits:

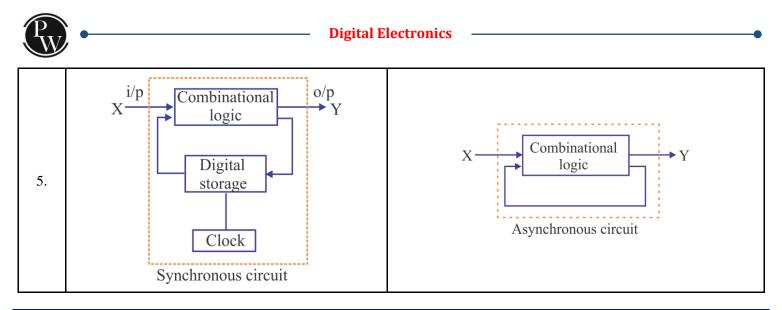

## 4.1.1. Synchronous Circuits

The sequential circuits which are controlled by a clock are called synchronous sequential circuits. These circuits get activated only when clock signal is present.

## 4.1.2. Asynchronous Circuits

The sequential circuits which are not controlled by a clock are called asynchronous sequential circuits, i.e. the sequential circuits in which events can take place any time the inputs are applied are called asynchronous sequential circuits.

# 4.2. Difference Between Synchronous and Asynchronous Sequential Circuits

| S.No. | Synchronous Sequential Circuits                                                                                        | Asynchronous Sequential Circuits                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 1.    | In synchronous circuits, the change in input signals<br>can affect memory elements upon activation of<br>clock signal. | In asynchronous circuits, change in input signals can affect<br>memory elements at any instant of time. |

| 2.    | In synchronous circuits, memory elements are clocked FF's.                                                             | In asynchronous circuits, memory elements are either<br>unlocked FF's or time delay elements.           |

| 3.    | The maximum operating speed of the clock depends<br>on time delays involved.                                           | Since the clock is not present, asynchronous circuits can operate faster than synchronous circuits.     |

| 4.    | They are easier to design.                                                                                             | More difficult to design.                                                                               |

#### GATE WALLAH COMPUTER SCIENCE & INFORMATION TECHNOLOGY HANDBOOK

# 4.3. Latches

Flip-flop is an electronic circuit or device which is used to store a data in binary form. Actually, flip-slop is a one-bit memory device and it can store either 1 or 0. Flip-flops is a sequential device that changes its output only when a clocking signal is changing. On the other hand, latch is a sequential device that checks all its inputs continuously and changes its outputs accordingly at any time independent of a clock signal. It refers to non-clocked flip-flops, because these flip-flops, because these flip-flops 'latch on' to a 1 or a 0 immediately upon receiving the input pulse.

# 4.3.1. General Block Diagram of a Latch or Flip-flop

Figure shown below is the general type of symbol used for a latch. In case of a flip-flop, a clock signal must be shown at input side. It has many inputs and two outputs, labelled Q and  $\overline{Q}$ . The Q output is the normal output of the latch and  $\overline{Q}$  is the inverted output.

**Note:** A flip-flop is said to be in HIGH state or logic 1 state or SET state when Q = 1, and in LOW state or logic 0 state or RESET state or CLEAR state when Q = 0.

## 4.3.2. Difference between Latches and Flip-flops

| S.No. | Latch                                                                                                                                                                                    | Flip-flop                                                                                                                                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.    | A latch is an electronic sequential logic circuit used to store information in an asynchronous arrangement.                                                                              | A flip-flop is an electronic sequential logic circuit used to<br>store information in a synchronous arrangement. It has<br>two stable states and maintains its states for an indefinite<br>period until a clock pulse is applied. |

| 2.    | One latch can store one-bit information, but output state changes only in response to data input.                                                                                        | One flip-flop can store one-bit data, but output state changes with clock pulse only.                                                                                                                                             |

| 3.    | Latch is an asynchronous device and it has no clock input.                                                                                                                               | Flip-flop has clock input and its output is synchronised with clock pulse.                                                                                                                                                        |

| 4.    | Latch holds a bit value and it remains constant until new inputs force it to change.                                                                                                     | Flip-flop holds a bit value and it remains constant until a clock pulse is received.                                                                                                                                              |

| 5.    | Latches are level-sensitive, and the output tracks the input<br>when the level is high. Therefore, as long as the level is<br>logic level 1, the output can change if the input changes. | Flip-flops are edge sensitive. They can store the input<br>only when there is either a rising or falling edge of the<br>clock.                                                                                                    |

# 4.4. Latch

A latch is a type of bistable logic device or multivibrator that is most often used in applications that require data storage. The main characteristics of latch is that the output is not dependent solely on the on the present state of the input but also on the proceeding output state.

Latches are sometimes used for multiplexing data onto a bus. For example, data being input to a computer from a external source have to share the data bus with data from other sources. When the data bus becomes unavailable to external source, the existing data must be temporarily stored, and hence the latches are placed between the external source and data bus.

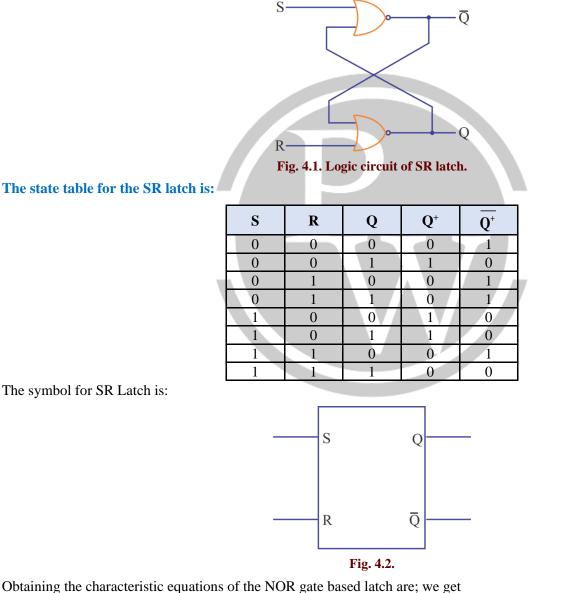

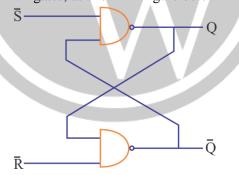

#### 4.4.1. SR Latch

For the SR latch (S stands for set and R for reset). The logic circuit for SR latch is shown in figure below:

blanning the characteristic equations of the NOK gate based fatch are, we get

$Q^{\scriptscriptstyle +} = \overline{R} \times S + \overline{R} \times Q = \overline{R} \times (S + Q) \text{ and } \overline{Q}^{\scriptscriptstyle +} = \overline{S} \times R + \overline{S} \times \overline{Q} = \overline{S} \times (S + \overline{Q})$

**Note:** It must be noted that the complementing  $Q^+$  does not yield  $\overline{Q}^+$ .

#### Hence, the truth table for SR latch is

| S | Q | $Q^+$ | $\overline{Q^+}$ |                                         |

|---|---|-------|------------------|-----------------------------------------|

| 0 | 0 | Q     | Q                | $\Rightarrow$ No change                 |

| 1 | 1 | 0     | 1                | $\Rightarrow$ Reset Q <sup>+</sup> to 0 |

| 1 | 0 | 1     | 0                | $\Rightarrow$ Set Q <sup>+</sup> to 1   |

| 1 | 1 | 0     | 0                | $\Rightarrow$ Forbidden state           |

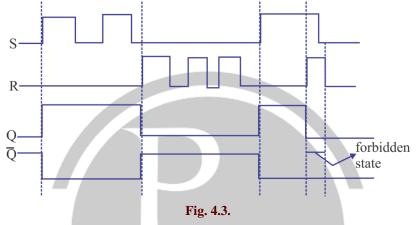

However, the forbidden state (S = R = 1) is considered a don't care state.

Consider a Timing diagram for SR latch

# 4.4.2. **S**R Latch:

An  $\overline{SR}$  latch can be implemented using NAND gates, as shown in figure below

Fig. 4.4. Logic circuit for  $\overline{SR}$  Latch

The  $\overline{SR}$  latch is said to be set-dominant 1, The symbol for  $\overline{SR}$  latch is shown below:

The truth table for  $\overline{\mathbf{S}}\overline{\mathbf{R}}$  latch is given as:

| $\overline{S}$ | R | $Q^+$ | $\overline{Q^+}$ |                                         |

|----------------|---|-------|------------------|-----------------------------------------|

| 1              | 1 | Q     | Q                | $\Rightarrow$ No change                 |

| 1              | 0 | 0     | 1                | $\Rightarrow$ Reset Q <sup>+</sup> to 0 |

| 0              | 1 | 1     | 0                | $\Rightarrow$ Set Q <sup>+</sup> to 1   |

| 1              | 1 | 1     | 1                | $\Rightarrow$ Forbidden state           |

Application of  $\overline{SR}$  latch: The application of  $\overline{SR}$  latch is in switch bouncing i.e. contact bounces of a push-button switch during its opening or closing can be eliminated by using  $\overline{SR}$  latch.

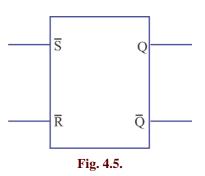

## 4.4.3. Gated SR Latch on Enable SR Latch or clocked SR Latch

A gated or level-sensitive SR latch uses a control signal C that can be used as a clock signal or can be used as enable input. The logic circuit diagram, symbol and truth is given as

0

0

$\Rightarrow$

Forbidden state

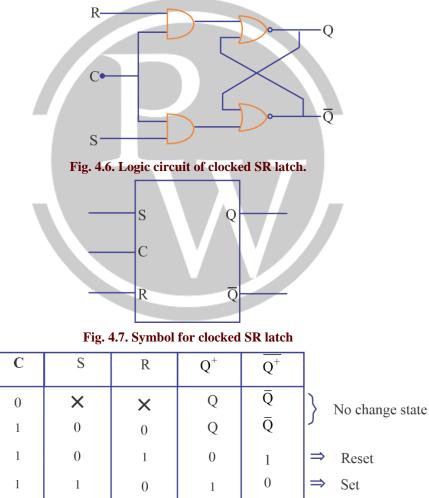

## 4.4.4. Gated $\overline{SR}$ Latch or enable $\overline{SR}$ Latch or clocked $\overline{SR}$ Latch

1

1

Gated  $\overline{SR}$  latch is implemented using two NAND gates and an  $\overline{SR}$  latch. The logic circuit diagram, symbol and truth is given as

1

The truth table of the gated SR latch based on a  $\overline{SR}$  latch:

| С | J | K | Q | $\overline{Q^+}$ |

|---|---|---|---|------------------|

| 0 | X | X | Q | Q                |

| 1 | 0 | 0 | Q | Q                |

| 1 | 0 | 1 | 0 | 1                |

| 1 | 1 | 0 | 1 | 0                |

| 1 | 1 | 1 | 1 | 1                |

The characteristic equation for SR flip-flop is given as

$$Q^+ = Q_{n+1} = S + \overline{R}Q_n = S + \overline{R}Q$$

# 4.5. Flip-Flops

Flip-flops are synchronous bistable devices also known as bistable multivibrator. Its output change its state only at a verified paint (i.e. leading or trailing edge) on the triggering input called the clock (CLK), i.e. changes in the output occur in synchronization with the clock.

Flip-flops are edge-triggered or edge-sensitive whereas gated latches are level-sensitive.

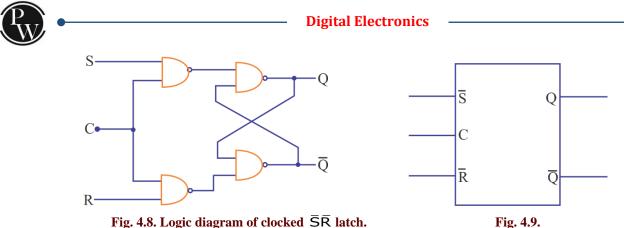

## 4.5.1. Edge-triggered flip-flop

An edge-triggered flip-flop changes its state either at positive edge (rising edge) or at negative edge (falling edge) of the check pulse.

There are two type of edge-triggered flip-flops. The key to identify an edge-triggered flip-flop is by its logic symbol by small triangle inside the block at the clock input C. This triangle is called the dynamic input indicator.

Positive edge triggered has no bubble at input C whereas negative edge triggered has bubble at input C.

Fig. 4.10. Positive edge triggered flip-flop.

Fig. 4.11. Negative edge-triggered flip-flop.

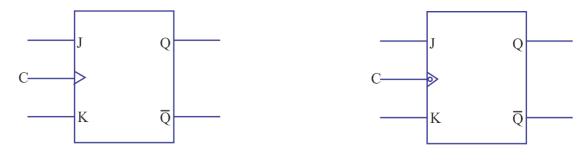

### 4.5.2. Basic JK flip-flop

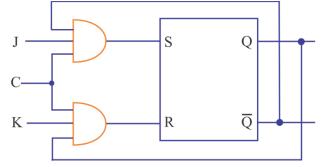

JK Flip-flop (J as a set input and K as a reset input) is the most versatile of the basic flip-flops. The logic circuit of the gated JK flip-flop is shown in figure below:

Fig. 4.12. Logic circuit diagram of clocked JK flip-flop.

The state table for the JK flip-flop is given as

|   |   | С | J        | K  | (                | <b>2</b>        | $\mathbf{Q}^+$      |     |

|---|---|---|----------|----|------------------|-----------------|---------------------|-----|

|   |   | 0 | X        | X  | 2                | X               | Q                   |     |

|   |   | 1 | <u> </u> | 0  | (                | 0               | 0                   |     |

|   |   | 1 | 0        | 0  |                  | 1               | 1                   |     |

|   |   | 1 | 0        | 1  | (                | 0               | 0                   |     |

|   |   | 1 | 0        | 1  |                  | 1               | 0                   |     |

|   |   | 1 | 1        | 0  |                  | 0               | 1                   |     |

|   |   | 1 | 1        | 0  |                  | 1               | 1                   |     |

|   |   | 1 | 1 1 0    |    | 1                |                 |                     |     |

|   |   | 1 | 1        | 1  |                  | 1               | 0                   | /   |

|   |   |   |          |    |                  |                 |                     | -   |

| ( | 7 | S | R        | Q+ | $\overline{Q}^+$ |                 |                     |     |

| ( | ) | Х | X        | Q  | Q                | 3 N             | } No change state   |     |

| 1 | l | 0 | 0        | Q  | Q                | -               |                     |     |

| 1 | l | 0 | 1        | 0  | 1                | $\Rightarrow F$ | $\Rightarrow$ Reset |     |

| 1 | l | 1 | 0        | 1  | 0                | $\Rightarrow$ S | $\Rightarrow$ Set   |     |

| 1 | l | 1 | 1        | 0  | 0                | $\Rightarrow$ F | Forbidden st        | ate |

Hence, the truth table becomes,

It should also be noted that when the inputs (J & K) are set to 1 and clock signal change to 1, then the feedback value of Q &  $\overline{Q}$  forced the flip-flop is toggle its value.

(i.e. to switch its state to its logical complement) hence, to ensure this operation in smooth fashion, the pulse width of the clock must be smaller than the propagation delay of the flip-flop. The characteristic equation of the JK flip-flop

$$Q_{n+1} = J\overline{Q}_n + \overline{K}Q_n \text{ or } Q^+ = J\overline{Q} + \overline{K}Q$$

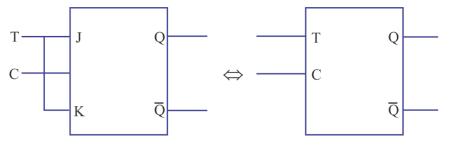

# 4.5.3. T-flip-flop

A JK flip-flop can be transformed into a T- flip-flop (T stands for Toggle). When T flip-flop is activated, its output changes its state at every time a pulse is applied to the input T.

The logic circuit of the gated T flip-flop is.

The state or characteristic table for T flip-flop is

| С   | Т | Q | $\mathbf{Q}^+$ |

|-----|---|---|----------------|

| 0   | X | X | Q              |

| 1   | 0 | 0 | 0              |

| - 1 | 0 | 1 | 1              |

| 1   | 1 | 0 | 1              |

| 1   | 1 | 1 | 0              |

As J = K = T, we obtain the characteristic equation as

$$Q^{\scriptscriptstyle +}\,=\,T\times \overline{Q}\times C + (\overline{T}+\overline{C})\times Q^{\scriptscriptstyle +}$$

If C = 1, the characteristic the equation is reduced to

$$Q^+ = T \oplus Q$$

If

$$C = 0$$

,  $Q^+ = Q$

Hence, the truth table of the T-flip flop is given as

| С | Т | $Q^+$ | $\overline{Q^+}$ |                                  |

|---|---|-------|------------------|----------------------------------|

| 0 | × | Q     | Q                |                                  |

| 1 | 0 | Q     | Q                | $\} \Rightarrow$ No change state |

| 1 | 1 | Q     |                  | ⇒ Toggle                         |

## 4.5.4. D Flip-Flop

D-flip-flop can be obtained by use of only two combinations of S-R or J-K flip-flop. It has only one input i.e. D-input or data input.

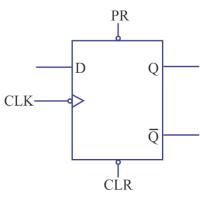

The logic symbol for D- flip-flop is given as

The truth table for D-flip-flop is

|                                                | Input | Output    |  |  |  |  |  |

|------------------------------------------------|-------|-----------|--|--|--|--|--|

|                                                | D     | $Q_{n+1}$ |  |  |  |  |  |

|                                                | 0     | 0         |  |  |  |  |  |

|                                                | 1     | 1         |  |  |  |  |  |

| The characteristic equation of D-flip-flop is: |       |           |  |  |  |  |  |

| $Q_{n+1}$                                      | = D   |           |  |  |  |  |  |

4.5.5. Excitation table of Flip-flops

The truth table of a flip-flop is sometimes referred as characteristic table as it specifies the operational characteristics of the flip-flop there may occurs some situations in which the present state and the next state of the circuit is desired and known. Then the designing of input conditions to as to fulfil the requirements of the circuit, there is a table called excitation table. It is very important and useful design aid for sequential circuit.

The excitation table for flip-flops:

| Present state  | Next state  | SR Flip-flop |   | JK Flip-flop |   | T Flip-flop | D Flip-flop |

|----------------|-------------|--------------|---|--------------|---|-------------|-------------|

| i resent state | Tient State | S            | R | J            | K | Т           | D           |

| 0              | 0           | 0            | × | 0            | × | 0           | 0           |

| 0              | 1           | 1            | 0 | 1            | × | 1           | 1           |

| 1              | 0           | 0            | 1 | ×            | 1 | 1           | 0           |

| 1              | 1           | ×            | 0 | ×            | 0 | 0           | 1           |

# 4.6. Operating Characteristics of Flip-Flops

## 4.6.1. Propagation Delay Time:

Propagation delay time is the time interval required after an input signal has been applied for the resulting output change to occur.

There are four categories of propagation delay times which are as follows:

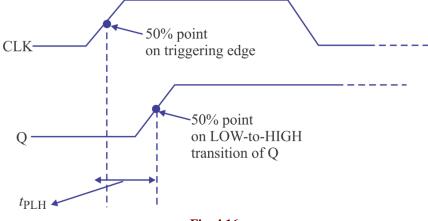

A. Propagation delay t<sub>PLH</sub>, it is measured from the triggering edge of the clock pulse to Low-to-High transition of the output.

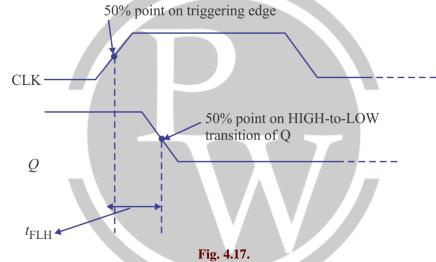

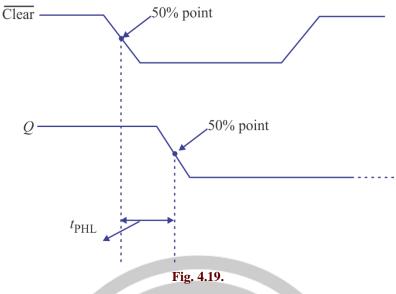

**B.** Propagation delay t<sub>PHL</sub>, it is measured from the triggering edge of the clock pulse to HIGH-to-LOW transition of the output.

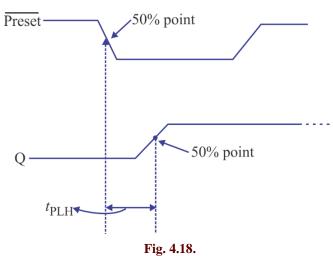

C. Propagation delay  $t_{PHL}$ , it is measured from the leading edge of the PRESET input to LOW-to-HIGH transition of the output.

**D. Propagation delay t<sub>PHL</sub>**, it is measured from the leading edge of the clear input to the HIGH-to-LOW transition of the output.

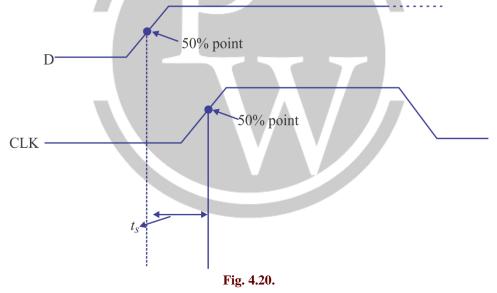

#### 4.6.2. Set-up time (*t*<sub>s</sub>)

It is the minimum time interval required for the logic levels (0 or 1) to be maintained constantly on the inputs (J, K or D) prior to the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flip-flop.

#### 4.6.3. Hold time (*t<sub>h</sub>*)

It is the time for which the data must remain stable after the triggering edge of the clock.

#### 4.6.4. Clock-pulse width

The minimum time duration for which the clock pulse must remain HIGH and LOW which are designed by manufacturers. Failure to clock pulse width results in unreliable triggering.

#### 4.6.5. Maximum clock frequency

The maximum clock frequency  $(f_{max})$  is the highest rate at which flip-flop can be reliably operated.

# 4.7. Applications of Flip-Flops

Some of the common applications of flip-flops are as follows:

- 1. Switch bouncing.

- 2. Registers.

- 3. Counters.

- 4. Memory elements.

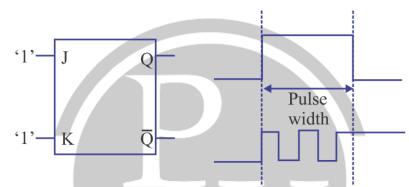

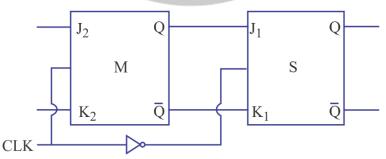

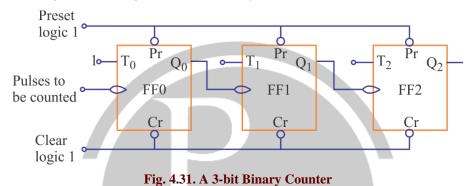

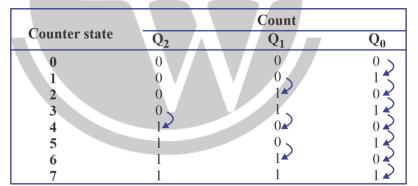

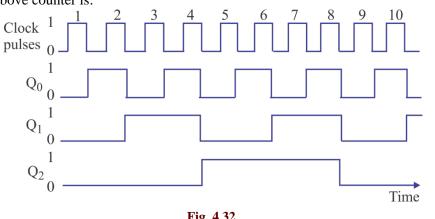

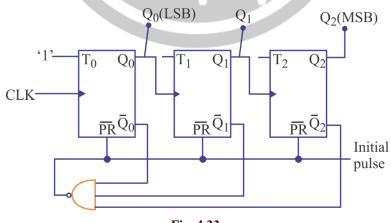

# 4.8. Race Around Condition